Московский Государственный Технический Университет

им. Н.Э.Баумана

Кафедра САПР(РК6)

Федорук А.В.

Методические указания по лабораторной работе

"Использование языка VHDL для моделирования цифровых

устройств на регистровом уровне"

Цель работы: освоение языка VHDL для использования в задачах

описания и анализа дискретных устройств (на регистровом уровне).

Практическая часть.

Пусть необходимо дать описание на языке VHDL счетчика по модулю 10, построенного

на JK-триггерах с запрещающими связями. Полученное описание должно быть

использовано для анализа поведения устройства средствами системы моделирования

и анализа Active-VHDL.

Используемый в примере счетчик описывается приведенной ниже логической

схемой:

JK-триггер также описывается логической схемой:

JK-триггер также описывается логической схемой:

Используемые для построения счетчика элементы могут быть представлены в

языке VHDL двояко:

Используемые для построения счетчика элементы могут быть представлены в

языке VHDL двояко:

-

функционально - путем задания выполняемых логических функций (с учетом

задержек сигналов).

-

структруно - путем задания их логической схемы.

Например, функциональное описание элемента 2И выглядит следующим образом:

entity and2 is

port (

x1: in BIT;

x2: in BIT;

o: out BIT );

end and2;

architecture and2 of and2 is

begin

o<= x1 and x2 after delay;

end and2;

где delay - задержка на элементе.

Структурное описание JK-триггера в базисе элементов 3И-НЕ выглядит

следующим образом:

entity jktrigger is

port (

R: in BIT;

S: in BIT;

J: in BIT;

C: in BIT;

K: in BIT;

Q: out BIT;

NQ: out BIT

);

end jktrigger;

architecture jktrigger of jktrigger is

component and_no_3

port (

x1: in BIT;

x2: in BIT;

x3: in BIT;

o: out BIT

);

end component;

signal Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8: BIT;

begin

E1: and_no_3

port map (Q8, J, C, Q1);

E2: and_no_3

port map (Q7, K, C, Q2);

E3: and_no_3

port map (S, Q1, Q4, Q3);

E4: and_no_3

port map (Q3, Q2, R, Q4);

E5: and_no_3

port map (Q2, Q3, Q1, Q5);

E6: and_no_3

port map (Q2, Q4, Q1, Q6);

E7: and_no_3

port map (S, Q5, Q8, Q7);

E8: and_no_3

port map (Q7, Q6, R, Q8);

Q <= Q7;

NQ <= Q8;

end jktrigger;

Рассматриваемый в примере счетчик на основе JK-триггеров и элементов 2И

описывается так:

entity counter is

port (

reset: in BIT;

clk: in BIT;

q: out BIT_VECTOR (4 downto 1)

);

end counter;

architecture counter of counter is

component jktrigger

port (

R: in BIT;

S: in BIT;

J: in BIT;

C: in BIT;

K: in BIT;

Q: out BIT;

NQ: out BIT

);

end component;

component and2

port (

x1: in BIT;

x2: in BIT;

o: out BIT

);

end component;

signal Q1, NQ1, Q2, NQ2, Q3, NQ3, Q4,NQ4,L1,L2,L3: BIT;

begin

T1: jktrigger

port map (Reset, '1','1',CLK,'1',Q1, NQ1);

T2: jktrigger

port map (Reset, '1', L1, CLK, Q1, Q2,NQ2);

T3: jktrigger

port map (Reset, '1', L2, CLK, L2, Q3,NQ3);

T4: jktrigger

port map (Reset, '1', L3, CLK, Q1, Q4, NQ4);

A1: and2

port map (Q1, NQ4, L1);

A2: and2

port map (Q1, Q2, L2);

A3: and2

port map (Q3, L2, L3 );

q(1) <= Q1;

q(2) <= Q2;

q(3) <= Q3;

q(4) <= Q4;

end counter;

Техническое задание:

Описать на языке VHDL счетчик по модулю 10 на синхронных двухступенчатых

JK-триггерах с запрещающими связями и промоделировать его работу.

-

Для того, чтобы создать новый проект, запустите Active-VHDL или,

если система уже запущена, воспользуйтесь пунктом New Design меню File.

С помощью New Design Wizard вы создадите необходимые для вашего проекта

файлы, библиотеки и шаблоны элементов:

Примечание 1: файлы, содержащие описание на языке VHDL, имеют,

как правило, расширение .vhd.

Примечание 2: библиотеки содержат необходимые для компиляции

и моделирования данные о проекте.

Примечание 3: шаблоны, генерируемые системой на данном этапе,

представляют собой описание интерфейса структурного элемента, подготовленное

для внесение в него описания архитектуры элемента, создаваемого пользователем.

-

В первом в порядке появления окне New Design Wizard задайте название вашего

проекта, его месторасположение в файловой системе операционной системы

и название сопутствующей ему библиотеки (по умолчанию используется то же

имя, что и для всего проекта).

-

Во втором окне New Design Wizard существует возможность выбора следующих

действий:

-

Create new source files now- создание описаний структурных элементов проекта

на языке VHDL с помощью New Design Wizard.

-

Add existing resource files - добавление к новому проекту уже существующих

файлов.

-

Import a design from Active-CAD - использование проектов, созданных в системе

Active CAD.

-

Create an empty design - создание проекта с пустыми файлами. Этот пункт

используется в том случае, если вы не хотите использовать возможности New

Design Wizard для создания шаблонов.

Для облегчения работы и ознакомления с возможностями системы выберите пункт

Create new source files now.

-

В следующем окне New Design Wizard вам будет необходимо описать элементы,

присутствующие в проекте. Для добавления элемента нажмите кнопку New, в

поле Entity name введите имя элемента, в поле Source Type - тип описания

элемента (в нашем случае для всех элемнтов необходимо выбрать тип VHDL

Code). Для каждого вновь создаваемого элемента необходимо задать входы

и выходы (в дальнейшем порты) с помощью окна Design Wizard - Ports, которое

вызывается кнопкой Ports. Для каждого порта (создание нового порта начинается

с нажатия кнопки New) надо указать его имя, направление и тип: вход - in,

выход - out, шина - buffer (размерность шины выбирается в поле Array Indexes,

где указывается максимальный и минимальынй номера портов в шине). Тип порта

устанавливается нажатием кнопки Types, где для обычного порта выбираем

тип BIT, а для шины - BIT_VECTOR. На данном этапе необходимо создать следующие

элементы:

-

3И-НЕ, из которых будет создаваться JK-триггер. Элемент имеет три входа

и один выход.

-

Сам триггер, имеющий следующие порты: входные R, S, J, C, K и выходные

Q и NQ.

-

2И, необходимые для построение счетчика. Элемент имеет два входа и один

выход.

-

Счетчик со следующими портами: входные Reset и CLK, выходная шина q(4,1)

-

В следующем окне New Design Wizard проверьте информацию о вашем проекте

и, в случае ее правильности, нажмите кнопку Finished (Готово). Если вы

хотите изменить какую-либо информацию, вернитесь на предыдущие этапы с

помощью кнопки Back (Назад)

-

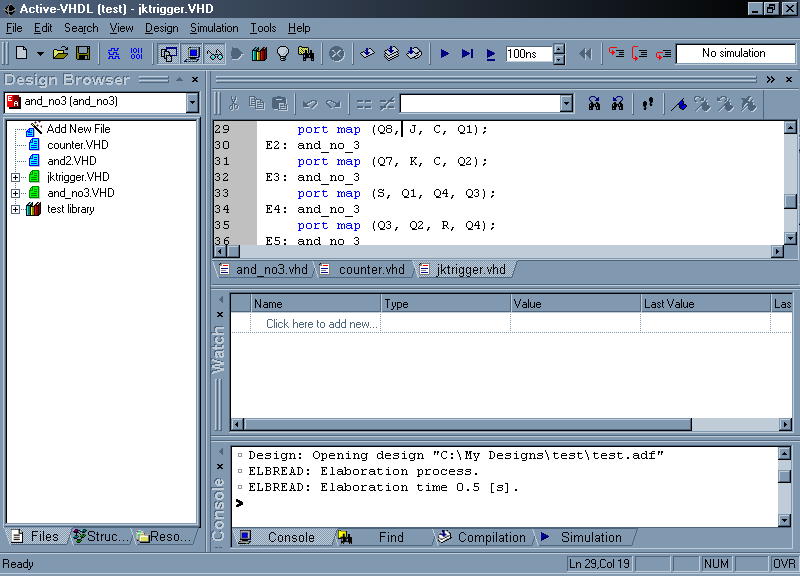

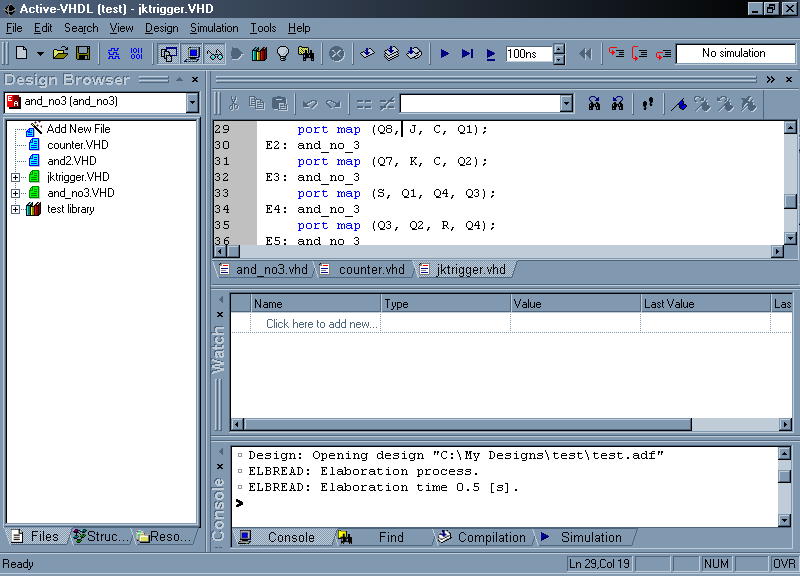

Итак,

исходные файлы для вашего проекта созданы. Файловую структуру проекта вы

можете увидеть в окне Design Browser (его можно включить, выбрав соответствующий

пункт в меню View), выбрав закладку (tab) Files. Если предыдущие этапы

были пройдены успешно, окно Design Browser должно выглядеть похоже на то,

что изображено на рисунке. Здесь присутствуют: пункт Add New File, которым

можно воспользоваться в случае, необходимости добавить еще какие-либо элементы

к вашему проекту (например, если вы забыли создать какой-то элемент на

предыдущих этапах), файл библиотеки test library, и 4 файла с VHDL-кодом

ваших элементов, созданным New Design Wizard. Цвета иконок в окне имеют

слудующий смысл:

Итак,

исходные файлы для вашего проекта созданы. Файловую структуру проекта вы

можете увидеть в окне Design Browser (его можно включить, выбрав соответствующий

пункт в меню View), выбрав закладку (tab) Files. Если предыдущие этапы

были пройдены успешно, окно Design Browser должно выглядеть похоже на то,

что изображено на рисунке. Здесь присутствуют: пункт Add New File, которым

можно воспользоваться в случае, необходимости добавить еще какие-либо элементы

к вашему проекту (например, если вы забыли создать какой-то элемент на

предыдущих этапах), файл библиотеки test library, и 4 файла с VHDL-кодом

ваших элементов, созданным New Design Wizard. Цвета иконок в окне имеют

слудующий смысл:

- синий - файлы еще не были откомпилированны или были изменены после

послденей компиляции;

- зеленый - файл был откомпилирован успешно;

- красно-желтый - обнаружение ошибки в компилировавшемся файле.

Следить за ходом работы над проектом, обнаруженными ошибками и другой информацией

вы можете в окне Console (включается через меню View).

-

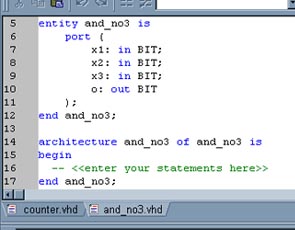

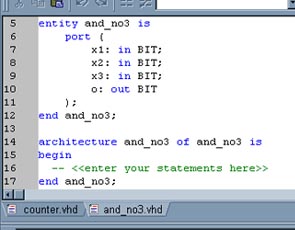

Для того,

чтобы посмотреть VHDL-код, созданный посредством New Design Wizard, изменить

или дополнить его, необходимо выбрать желаемый файл, нажать правую кнопку

мыши и в появившемся меню выбрать пункт Open (Открыть). Во вновь открывшемся

окне вы увидите описание элемента, сгенерированное New Design Wizard. Как

видно из рис., описаны только порты элемента, его же поведение (функциональность)

необходимо описать самостоятельно, т.е. вставить необходимый код вместо

надписи "-- <<enter your statements here>>".

Элементы самого нижнего уровня (3И-НЕ и 2И) необходимо описать функционально.

Например, для элемента 3И-НЕ вставляемый текст может выглядеть следующим

образом: o<= not (x1 andx2

and

x3) after delay;

Для того,

чтобы посмотреть VHDL-код, созданный посредством New Design Wizard, изменить

или дополнить его, необходимо выбрать желаемый файл, нажать правую кнопку

мыши и в появившемся меню выбрать пункт Open (Открыть). Во вновь открывшемся

окне вы увидите описание элемента, сгенерированное New Design Wizard. Как

видно из рис., описаны только порты элемента, его же поведение (функциональность)

необходимо описать самостоятельно, т.е. вставить необходимый код вместо

надписи "-- <<enter your statements here>>".

Элементы самого нижнего уровня (3И-НЕ и 2И) необходимо описать функционально.

Например, для элемента 3И-НЕ вставляемый текст может выглядеть следующим

образом: o<= not (x1 andx2

and

x3) after delay;

-

Откомпилируйте

готовый код элемента (кнопка Compile на панели инструментов или пункт Compile

в контекстном меню). Если в коде есть ошибки (иконка файла стала желто-красной),

найдите их с помощью окна Console, исправьте и откомпилируйте заново, пока

иконка файла не станет зеленым.

Откомпилируйте

готовый код элемента (кнопка Compile на панели инструментов или пункт Compile

в контекстном меню). Если в коде есть ошибки (иконка файла стала желто-красной),

найдите их с помощью окна Console, исправьте и откомпилируйте заново, пока

иконка файла не станет зеленым.

-

Для того, чтобы проверить правильность работы элемента, промоделируем его

и построим временные диаграммы. Для этого:

-

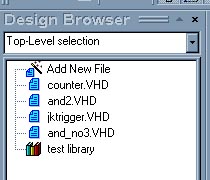

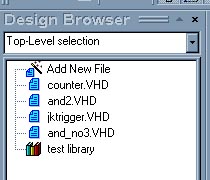

Выберем рассматриваемый элемент как верхний уровень в верхней части Design

Browser (Top-Level selection) и перейдем на закладку Structure окна Design

Browser. Здесь вы увидите структуру элемента, например, какие элементы

нижнего уровня он включает. Пока рассматриваемый элемент сам является элементом

низшего уровня. В нижней части окна Design Browser теперь находится информацию

о портах элемента и значениях сигналов на портах. Так как моделирование

еще не проводилось, значения не определены.

-

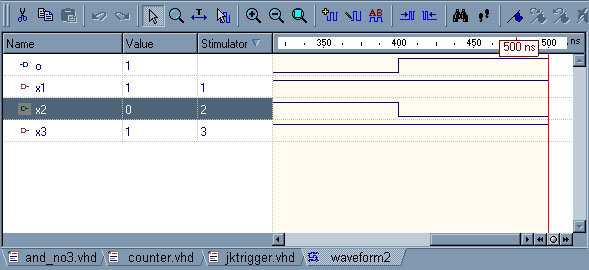

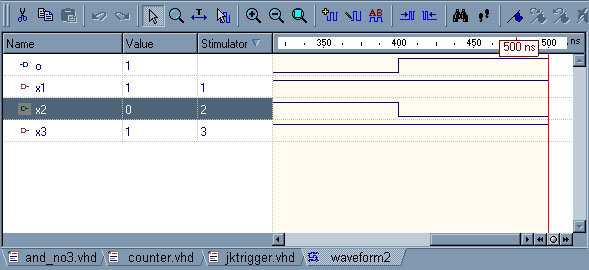

Для создания

новой временной диаграммы нажмите кнопку Create New Waveform. Откроется

новое окно. "Перетащите" из нижней части Design Browser в поле Name нового

окна имена тех сигналов, для которых вы хотите построить временные диаграммы.

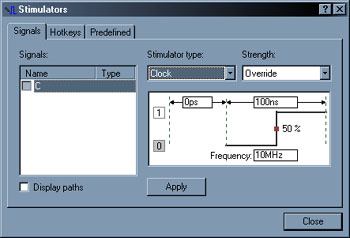

Для того, чтобы задать входные сигналы, необходимо нажать кнопку

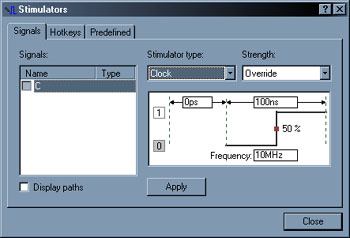

Для создания

новой временной диаграммы нажмите кнопку Create New Waveform. Откроется

новое окно. "Перетащите" из нижней части Design Browser в поле Name нового

окна имена тех сигналов, для которых вы хотите построить временные диаграммы.

Для того, чтобы задать входные сигналы, необходимо нажать кнопку  Stimulators

или выбрать пункт контекстного меню c тем же названием. Для каждого сигнала

необходимо установить его тип и силу. Тип устанавливается в поле Stimulator

type окна Stimulators. Возможные типы сигналов перечислены ниже.

Stimulators

или выбрать пункт контекстного меню c тем же названием. Для каждого сигнала

необходимо установить его тип и силу. Тип устанавливается в поле Stimulator

type окна Stimulators. Возможные типы сигналов перечислены ниже.

-

Clock - сигнал в виде последовательности одинаковых импульсов. Параметры

(частота импульсов, время начала) устанавливаются в полях на появившейся

картинке.

-

Custom - позволяет задать произвольную форму сигнала.

-

Formula - форма сигнала задается формулой. Формула выглядит следующим образом:

значение

[ время {, значение время}[ -r период]]. Например, формула 0 0, 1

80 ns -r 100 ns означет, что сигнал начинается с логического "0", а с 80-й

нс - переходит к логической "1", на 100-й - опять переходит в "0" и т.д.

-

Hotkey - позволяет привязать к сигналу клавишу, при нажатии которой сигнал

будет переключаться. Для этого надо в поле Press new hotkey ввести желаемую

клавишу. Задействованные клавиши и переключаемые ими значения можно посмотреть,

выбрав закладку Hotkeys.

-

Predefined - позовляет воспользоваться шаблонами, уже определенными в системе

Active-VHDL.

-

Value - позволяет задать конкретное значение для сигнала.

Удобнее всего будет, если вы выберите для всех трех входных сигналов тип

Hotkey. Силу (Force) для всех сигналов следует определить как Override.

-

После того, как вы определили все входные сигналы, можно приступать к моделированию.

Установите желаемый шаг модельного времени и нажмите кнопку Run For. Для

выбранного промежутка времени будет построена временная диаграмма. Меняя

с помощь горячих клавиш значения входных сигналов и наблюдая за выходным,

сделайте вывод о правильности работы элемента.

-

Повторите процесс моделирования для всех элементво нижнего уровня (2И).

-

После того, как все элементы нижнего уровня созданы и промоделированы,

можно создавать элементы верхних уровней. Покажем этот процесс на примере

создания JK-триггера из элементов 3И-НЕ. Для этого откройте код, созданный

New Design Wizard для триггера (аналогично тому, как это делается для элементов

нижнего уровня) и структурно опишите архитектуру триггера. Повторите процедуру

компиляции кода и построения временных диаграмм, как описано ранее. При

этом не забудьте выбрать в качетсве верхнего уровня проектируемый элемент.

-

Так же, как в п.7 промоделируйте элемент самого верхнего уровеня - счетчик.

При этом при построении временной диаграммы для всех входов, кроме CLK,

выберите тип Hotkey, а для CLK - тип Clock с частотой, которая учитывает

задержку, которую вы задали для элементов нижнего уровня.

Отчет по лабораторной работе должен содержать схемы моделируемых элементов

и временные диаграммы, полученные в результате проведения моделирования

в системе Active-VHDL.

Рекомендуемая литература.

-

Армстронг Дж.Р. Моделирование цифровых систем на языке VHDL: Пер. с англ./М.:

Мир, 1992.-175 с.

-

Active-VHDL Series. Getting Started Guide.- Poland: Aldec, Inc.,1998.-202

pp.

-

www.aldec.com

Итак,

исходные файлы для вашего проекта созданы. Файловую структуру проекта вы

можете увидеть в окне Design Browser (его можно включить, выбрав соответствующий

пункт в меню View), выбрав закладку (tab) Files. Если предыдущие этапы

были пройдены успешно, окно Design Browser должно выглядеть похоже на то,

что изображено на рисунке. Здесь присутствуют: пункт Add New File, которым

можно воспользоваться в случае, необходимости добавить еще какие-либо элементы

к вашему проекту (например, если вы забыли создать какой-то элемент на

предыдущих этапах), файл библиотеки test library, и 4 файла с VHDL-кодом

ваших элементов, созданным New Design Wizard. Цвета иконок в окне имеют

слудующий смысл:

Итак,

исходные файлы для вашего проекта созданы. Файловую структуру проекта вы

можете увидеть в окне Design Browser (его можно включить, выбрав соответствующий

пункт в меню View), выбрав закладку (tab) Files. Если предыдущие этапы

были пройдены успешно, окно Design Browser должно выглядеть похоже на то,

что изображено на рисунке. Здесь присутствуют: пункт Add New File, которым

можно воспользоваться в случае, необходимости добавить еще какие-либо элементы

к вашему проекту (например, если вы забыли создать какой-то элемент на

предыдущих этапах), файл библиотеки test library, и 4 файла с VHDL-кодом

ваших элементов, созданным New Design Wizard. Цвета иконок в окне имеют

слудующий смысл: Для того,

чтобы посмотреть VHDL-код, созданный посредством New Design Wizard, изменить

или дополнить его, необходимо выбрать желаемый файл, нажать правую кнопку

мыши и в появившемся меню выбрать пункт Open (Открыть). Во вновь открывшемся

окне вы увидите описание элемента, сгенерированное New Design Wizard. Как

видно из рис., описаны только порты элемента, его же поведение (функциональность)

необходимо описать самостоятельно, т.е. вставить необходимый код вместо

надписи "-- <<enter your statements here>>".

Элементы самого нижнего уровня (3И-НЕ и 2И) необходимо описать функционально.

Например, для элемента 3И-НЕ вставляемый текст может выглядеть следующим

образом: o<= not (x1 andx2

and

x3) after delay;

Для того,

чтобы посмотреть VHDL-код, созданный посредством New Design Wizard, изменить

или дополнить его, необходимо выбрать желаемый файл, нажать правую кнопку

мыши и в появившемся меню выбрать пункт Open (Открыть). Во вновь открывшемся

окне вы увидите описание элемента, сгенерированное New Design Wizard. Как

видно из рис., описаны только порты элемента, его же поведение (функциональность)

необходимо описать самостоятельно, т.е. вставить необходимый код вместо

надписи "-- <<enter your statements here>>".

Элементы самого нижнего уровня (3И-НЕ и 2И) необходимо описать функционально.

Например, для элемента 3И-НЕ вставляемый текст может выглядеть следующим

образом: o<= not (x1 andx2

and

x3) after delay;